# **HSDLC**

## **HDLC & SDLC Protocol Controller**

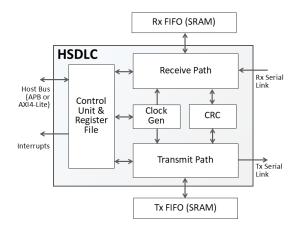

The HSDLC IP core implements a controller for the High-Level Data Link Control (HDLC) and the Synchronous Data Link Control (SDLC) protocols. It is based on the Intel® 8XC152 Global Serial Channel (GSC) working in SDLC mode and adds features to support HDLC or proprietary frame transmission under host processor control.

The core operates as a peripheral to a host processor, and is easy to integrate with both modern and legacy processors. Control and status registers are accessible via an APB or a generic 80C51-like bus interface, and a comprehensive set of interrupt signals facilitates interrupt-based operation.

The controller's great flexibility enables a variety of serial link setups. It provides two independent interfaces, one for transmitting and one for receiving data. Both interfaces provide control signals for the link drivers to support both full- and half-duplex operation. The controller can be programmed to use hardware flow control signals (RTS/CTS) and it can also detect collisions. The baud rate is programmable and limited only by the link drivers and the core's clock frequency. The core derives the receive clock from the received serial data, or uses an externally provided receive clock.

The HSDLC is available in two versions: Normal, and Safety-Enhanced. The Safety-Enhanced version implements triple-modular redundancy (TMR) to provide full immunity to single-bit upsets and errors and complies to Design Assurance, Level A (DAL-A) of the DO-254 standard.

The HSDLC controller core is designed for reuse and is rigorously verified and scan-ready. Although designed to manage serial links, the core contains no latches or tri-states, and is fully synchronous with a single clock domain. The core is available in Verilog RTL or as a targeted FPGA netlist. Deliverables provide everything required for a successful implementation, including sample scripts, an extensive testbench, and comprehensive documentation.

#### **Applications**

The HSDLC controller core can be used in telecommunication equipment supporting HDLC-based protocols such as X.25 or ISDN-D. It can also be used to implement serial interfaces between processors and peripherals.

## **Block Diagram**

#### **FEATURES**

- Controller for both the SDLC and HDLC (ISO 13239) transmission protocols

- Based on the Intel® 8XC152

Global Serial Channel (GSC), operating in SDLC Mode

- Additional features support HDLC and proprietary serial protocols.

- Safety Enhanced DO-254/DAL-A Version (Optional)

- Implements TMR for all internal registers

- Delivered with a complete DO-254 Certification Data Package

- Flexible Frame Formatting

- Programmable preamble pattern and preamble length

- Programmable inter-frame space

- Single- or double-byte address field

- Address filtering allowing multicast and broadcast

- Raw transmit and receive testing modes

- Back-to-back transmit & back-toback receive

- NRZ, NRZI, Bi-Phase-S, and Manchester Data Encoding & Decoding

- Bit Stuffing and Bit Stripping

- 16-bit (CRC-16, CCITT or IBM) and 32-bit (CRC-32) frame check sequence

- CRC, Bit Stuffing/Stripping, and abort and idle sequences detection can be independently enabled/disabled

- Receiver FIFO Packet counter

- Flexible Serial Link Interface

- Full or Half Duplex

- o Programmable Baud Rate

- Modem Controls (RTSn/CTSn)

- Collision detection

- Internal baud generator, or external transmit clock with strobe

- Automatic receive clock recovery, or external receive clock with strobe

- Easy to Integrate

- Suitable for interrupt-based or polling-based operation

- Configurable size, Transmit & Receive FIFOs

- 80XC152-like control status registers

- APB or AXI4-Lite

## **Support**

The core as delivered is warranted against defects for ninety days from purchase. Thirty days of phone and email technical support are included, starting with the first interaction. Additional maintenance and support options are available.

## **Implementation Results**

HSDLC core reference designs have been evaluated in a variety of technologies. The following are sample results, for the normal version of the core configured with Tx and Rx FIFOs. FIFOs are 3 bytes each and implemented with flip-flops.

| Technology    | Area<br>(eq. NAND2 gates) | Max. Freq.<br>(MHz) |

|---------------|---------------------------|---------------------|

| TSMC 65nm LP  | 7,575                     | 400                 |

| TSMC 40nm G   | 5,594                     | 1,200               |

| TSMC 28nm HPM | 4.588                     | 1,800               |

## Verification

The core has been verified through extensive synthesis, place and route, and simulation runs. It has been embedded in several shipping customer products, and is proven in both ASIC and FPGA technologies.

## **Deliverables**

The core is available in synthesizable RTL and FPGA netlist forms, and includes everything required for successful implementation, including a sophisticated self-checking testbench, simulation scripts, test vectors, and expected results, synthesis scripts and comprehensive user documentation.

The deliverables for the safety-enhanced version include a complete DO-254/DAL-A Certification Data Package.