# **I2CSPI-CTRL**

# I2C and SPI Master/Slave Controller

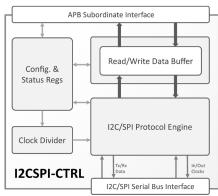

AMD27 The I2CSPI-CTRL is a compact and versatile serial interface controller supporting both SPI (Serial Peripheral Interface) and I2C (Inter-Integrated Circuit) protocols. Its low silicon resource requirement makes it suitable for area-constrained and low-power applications, while its software compatibility with Microchip's MSSP periph-

eral eases use and software integration.

In SPI mode, the I2CSPI-CTRL controller can operate as either a master or slave, offering fullduplex communication. In master mode, it initiates data transfers and controls the clock (SCK), while in slave mode, it operates under the control of an external master device. The I2CSPI-CTRL supports configurable clock polarity and operates in the four standard SPI modes (0, 1, 2, 3).

In I2C mode, the I2CSPI-CTRL supports standard, and fast mode with transfer rates of up to 400khz, with both 7-bit and 10-bit addressing. It

can function as either a master or a slave, with the capability to manage multiple addressing modes and clock stretching. In master mode, the I2CSPI-CTRL initiates communication, sends addresses, and manages data transfer timing. In slave mode, it responds to addresses sent by an external master, acknowledges reception, and sends data upon request. The I2CSPI-CTRL also supports general call addressing and SMBUS protocols, making it suitable for various applications.

The I2CSPI-CTRL core is designed for ease of use and integration and adheres to the industry's best coding and verification practices. The core's control and status registers (CSR) are accessed through a 32-bit AMBA<sup>®</sup> APB interface. The design contains no latches or tri-states and is fully synchronous with a single clock domain making technology mapping straightforward. The I2CSPI-CTRL core is rigorously verified and silicon-proven. It is available in LINTclean System Verilog source code or as a targeted FPGA netlist. Its deliverables include a testbench, comprehensive documentation, and sample simulation and synthesis scripts.

# Applications

The I2CSPI-CTRL module is designed for easy integration into various systems, offering flexibility for designers utilizing SPI or I2C. Its applications range from consumer electronics to industrial automation, including LIDAR distance measurement, mmWave sensors, gesture recognition, biometric sensors, and magnetometers. The I2CSPI-CTRL 's compact and resource-optimized design, along with its dual support for SPI and I2C, makes it an ideal choice for a wide range of applications in both ASIC and FPGA environments.

# Support

The core as delivered is warranted against defects for ninety days from purchase. Thirty days of phone and email technical support are included, starting with the first interaction. Additional maintenance and support options are available.

# **Implementation Results**

The I2CSPI-CTRL synthesizes to approximately 230 LUTs and can be mapped to any AMD FPGA device (provided sufficient silicon resources are available).

#### FEATURES

#### Compact and Versatile

- Only 230 LUTs

- I2C and SPI Master and Slave

#### SPI Interface

- Compliant to the SPI de-facto standard

- Master/Slave modes

- Full-Duplex Communication

- Interrupt Support

- Configurability

- Clock Polarity

- Clock Phase

#### **I2C Interface**

- Compliant with Philips I2C standard

- I2C Bus Speeds:

- Standard-Mode (Sm): up to 100kbit/s, bidirectional

- Fast-mode (Fm): up to 400kbit/s, bidirectional

- Master/Slave modes

- 7-bit and 10-bit addressing

- Supports single or multi-master buses

- Clock-Stretching to allow fastmaster slow-slave communication

- SMBUS support

#### Easy to Use and Integrate

- Standardized 32-bit APB interface

- Single interrupt line with maskable sources

- Software-compatible with Microchip's MSSP peripheral

- Configurable glitch filter

- Singe-clock, LINT-clean design

#### Deliverables

- Synthesizable System Verilog source code or targeted FPGA netlist

- Testbench and sample test cases

- Simulation and Synthesis scripts

- Documentation