Silicon IP Cores

Lossless Data Compression

Reduce data storage and bandwidth requirements

CAST offers a family of silicon IP cores for GZIP/ZLIB/Deflate lossless compression and decompression, as well as a LZ4/Snappy decompression core. The IP cores of the family are highly configurable to allow fine-tuning of its compression efficiency, throughput, size and latency to match the requirements of the end application. These IP cores can be mapped in ASIC or FPGA, and have been used to reduce the cost and power for data storage and transfer within SoCs, as well as in big-data servers.

- High-speed hardware compression for LZ4 and Snappy formats

- High-speed hardware decompression for LZ4 and Snappy formats

- Scalable throughput over 100Gbps

- Low latency, approximately 30 clock cycles

- GZIP, ZLIB, and Deflate compression

- Highly configurable core allows different levels of compression efficiency, throughput, latency and size for different configurations

- Capable of 100Gbps+ & gzip -6 compression level

- Decompression of GZIP, ZLIB, and Deflate files

- Limited versions allow optimizing area and/or latency

- Scalable throughput by multiple core instantiations

Designed for easy integration, all cores are equipped with AMBA® AXI4-Stream interfaces, which can be optionally bridged to AXI4 memory mapped using one of the following cores:

- MM2ST: AHB/AXI4-Lite to AXI4-Stream bridge

- AXI4-SGDMA: AXI4 to/from AXI4-Stream Scatter-Gather DMA

- AXI4-DMA: AXI4 to/from AXI4-Stream DMA

Read about them below, see each core's product page, and contact Sales to learn more or discuss how we can support your evaluation.

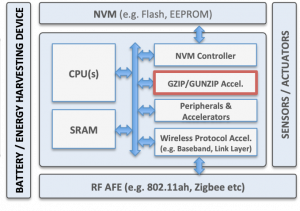

Compression can be used to significantly reduce the energy consumption related to the power-hungry NVM and RF module of your design:

- NVM: Storing compressed (instead of uncompressed) firmware and decompressing on-the-fly at boot time reduces boot/wake-up energy and time.

- RF: Transmitting compressed (instead of uncompressed data) over your RF link, reduces the active time for your RF front-end, and the energy related to it.

Read more in this white paper: Firmware Compression for Lower Energy and Faster Boot in IoT Devices.

GZIP/ZLIB/Deflate Data Compressor

GUNZIP/ZLIB/Inflate Data Decompression

LZ4/Snappy Data Compressor

LZ4/Snappy Data Decompressor