Silicon IP Cores

PCI-HB-AHB

PCI to AMBA AHB Host Bridge

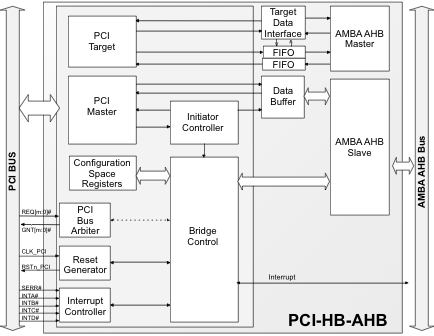

This PCI Host Bridge IP core enables data transfers between an AMBA® AHB host processor bus system and PCI bus based devices.

The bridge enables higher utilization of the bus’ available bandwidth by prefetching PCI data and buffering AHB data, and allows the host to initiate PCI accesses or to respond to transactions initiated by other PCI devices.

The core complies with the PCI bus specification versions 3.0 and 2.3, and can act as a PCI master and target. Furthermore, it implements PCI bus arbitration, supporting up to seven PCI bus agents, PCI reset signal generation, and all types of PCI transactions provisioned by the standard.

The host connects to the bridge via master and slave 32-bit AMBA/AHB bus interfaces. The AHB slave interface allows the host to access the status and control registers and to initiate PCI Transfers, while data from the PCI target is communicated to the host via the AHB master interface.

The PCI-HB-AHB builds on more than 15 years of CAST PCI IP expertise and has been designed for straightforward reuse, with proven design practices that ensure easy integration and smooth technology mapping. The core is available in synthesizable RTL or as a targeted FPGA netlist, and is delivered with everything required for rapid and successful integration and implementation.

The core has been verified through extensive simulation, rigorous code coverage measurements and it has been proven in FPGA and ASIC designs.

Support

The core as delivered is warranted against defects for ninety days from purchase. Thirty days of phone and email technical support are included, starting with the first interaction. Additional maintenance and support options are available.

Deliverables

The core is available in ASIC (synthesizable HDL) and FPGA (netlist) forms, and includes everything required for successful implementation. The ASIC version includes:

- HDL RTL source code

- Sophisticated HDL Testbench

- Simulation script, vectors, expected results, and com-parison utility

- Synthesis script

- Comprehensive user documentation, including detailed specifications and a system integration guide

The PCI-HB-AHB can be mapped to any ASIC technology or FPGA device (provided sufficient silicon resources are available). The following table provides sample performance and resource utilization data. Please contact CAST to get characterization data for your target configuration and technology.

|

ASIC |

Cell Area |

NAND2 Area (um^2) |

Approx. Area |

Frequency |

| TSMC 65 nm | 31,778 | 1.6 | 19,861 | 66 |

| TSMC .09 µm | 49,920 | 2.8224 | 17,700 | 66 |

| TSMC .13 µm | 98,308 | 5.0922 | 19,300 | 66 |

| TSMC .18 µm | 206,616 | 9.9792 | 20,700 | 66 |

Features List

PCI Host Bridge

- Enables data communication between the Host Processor residing on an AHB bus and devices on the PCI bus

- PCI I/O space and memory space are mapped directly to the AMBA AHB memory space

- PCI Interrupt and System Errors are propagated as interrupts to the host

- PCI Configuration registers are accessible from both PCI and host directions

- Advanced PCI data prefetching and AHB data buffering for improved bus bandwidth utilization

- Asynchronous AMBA/AHB and PCI clocks

PCI Interface

- PCI specification 3.0 and 2.3 compliant

- 33 MHz

- 32-bit bus width

- 32-bit address space

- Parity generation and parity error detection

- PCI Master & Target support all types of transactions:

- Configuration space read/write

- Memory space read/write

- I/O Space read/write

- Interrupt acknowledge (optional)

- Special cycles (optional)

- PCI reset generator

- PCI bus arbiter

- Up to 7 external bus agents

- Flexible priority schemes

- Agent malfunction detection and reporting

AHB Interface

- 32-bit AMBA/AHB v2.0 host interface

- AHB Slave enables host to initiated PCI transaction and access configuration registers

- AHB Master delivers data from the PCI target interface to the host