Silicon IP Cores

PNG-D

PNG Lossless Compression Decoder

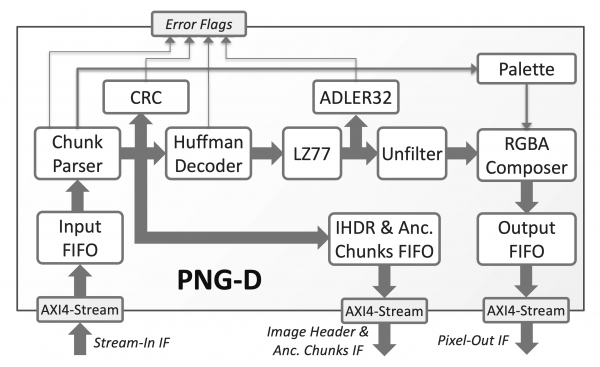

The PNG-D core implements a lossless image decompression engine compliant with the Portable Network Graphics (PNG) file format specified in the ISO/IEC 15948 and RFC 2083 standards.

The decoder core can decompress greyscale, truecolor, and palette-based PNG images with 8 and 16 bits per color. The core supports alpha channel transparency¬ and all the filters and DEFLATE compression options specified by the PNG standard. The core does not currently support interlaced mode and images with under 8 bits per color, but these can be added on request.

The easy-to-use PNG-D core operates on a standalone basis, parsing the image header and decompressing image data without a host processor's assistance. PNG-D accepts compressed data and outputs pixel data via AXI4-Stream interfaces. A separate dedicated interface provides the system with the image header and any ancillary chunks to prepare the decoded images for further processing and/or display. Moreover, the core detects, reports, and automatically recovers from various errors in the input files.

The core is designed with industry best practices, and its reliability has been proven through rigorous verification. The deliverables include a complete verification environment and a bit-accurate software model.

A wide range of SoC designs using PNG files can benefit from this custom-hardware decompression engine's high performance and lower power. End applications range from wearables to data-center acceleration and aerospace imaging.

The PNG-D is a digital core and can be mapped to any ASIC technology. The following are sample implementation results. These sample results do not represent the minimum area or the fastest clock speed for the PNG-D core. Please contact CAST to get accurate characterization for your target technology and throughput requirements.

| ASIC Technology | Logic | Memory* (kbits) |

Freq. (MHz) | |

|---|---|---|---|---|

| Area (um^2) | Eq. NAND2 Gates | |||

| TSMC 7nm tsmc7-sch240mc-c11-svt-675v-125c |

1,339 | 24,470 | 264 | 800 |

| TSMC 16nm tsmc16-sc7-svt-c16-ssgnp-125c |

4,049 | 23,432 | 264 | 700 |

*Memory requirements exclude the image-line buffer. Memory size can be significantly reduced by limiting the maximum size of the LZ77 History window and FIFO sizes.

The PNG-D is a digital core and can be mapped to any Altera® FPGA device (provided sufficient resources are available). The following are sample implementation results. These sample results do not represent the minimum area or the fastest clock speed for the PNG-D core. Please contact CAST to get accurate characterization for your target device and throughput requirements.

| Target Family/Device | Logic Resources |

Memory Resources * |

Freq. (MHz) |

|---|---|---|---|

| AGILEX™ Speed grade -2 |

2,661 ALMs | 35 RAMB | 150 |

| Arria® 10 GX Speed grade -1 |

2,327 ALMs | 35 RAMB | 100 |

* Memory requirements include an 8kB pixels image-line buffer. Memory size can be significantly reduced by limiting the maximum size of the LZ77 History window and the image line, and the FIFO sizes.

The PNG-D is a digital core and can be mapped to any AMD® FPGA device (provided sufficient resources are available). The following are sample implementation results. These sample results do not represent the minimum area or the fastest clock speed for the PNG-D core. Please contact CAST to get accurate characterization for your target device and throughput requirements.

| Target Family/Device | Logic Resources |

Memory Resources * |

Freq. (MHz) |

|---|---|---|---|

| ARTIX® UltraScale+™ xcau20p-sfvb784-2 |

4,533 LUTs | 15 BRAM | 153 |

| KINTEX® UltraScale+™ xcku15pffve1760-3 |

4,590 LUTs | 15 BRAM | 181 |

| KINTEX® UltraScale™ xcku085flvb1760-1 |

4,590 LUTs | 15 BRAM | 105 |

* Memory requirements include an 8kB pixels image-line buffer. Memory size can be significantly reduced by limiting the maximum size of the LZ77 History window and image line, and the FIFO sizes.

The PNG-D is a digital core and can be mapped to any Lattice FPGA device (provided sufficient resources are available). The following are sample implementation results. These sample results do not represent the minimum area or the fastest clock speed for the PNG-D core. Please contact CAST to get accurate characterization for your target device and throughput requirements.

| Target Family/Device | Logic Resources |

Memory Resources * |

Freq. (MHz) |

|---|---|---|---|

| ECP5 lfd2nx-40cabga256 |

2,691 Slices 1 Mult18 |

27 EBR | 34 |

| Certus-NX lfe5u-45fcabga381 |

3,165 Slices 1 Mult18, 2 Mult9 |

11 EBR 2 LRAM |

44 |

* Memory requirements include an 8kB pixels image-line buffer. Memory size can be significantly reduced by limiting the maximum size of the LZ77 History window and the image line, and the FIFO sizes.

Engineered by IObundle

Features List

PNG Image Format Support

- Compliant with the ISO/IEC 15948 and RFC 2083 standards

- All chunk types

- Ancillary chunks are extracted and broadcasted to the system

- All color types

- Greyscale with or without alpha

- Truecolor with or without alpha

- Indexed (Palette-Based)

- 8-bit & 16-bit per color channel

- Support for under 8 bits per color channel available on request

- All five filters: Paeth, Average, Up, Sub and None

- Both Dynamic and Static Huffman Tables

- Interlacing and less than 8-bit per color can be added on request

Easy to Use and Integrate

- Requires no programming or control from the host

- AXI4-Stream Interfaces for image and compressed data

- Dedicated AXI4-Stream interface for passing image format information and ancillary chunks to the system

- Detects, reports, and automatically recovers from the following error types: CRC or Adler mismatch, image or zlib header syntax error, and unsupported image format

- Optional wrappers bridge the AXI4-Stream to AXI4 memory-mapped interfaces

High-Throughput

- Over 100 Mpixels/s in mid-range FPGAs, and several hundreds of Mpixels/s on modern ASIC technologies

- Nominal throughput:

- 1 pixel/cycle for 8-bit greyscale

- 0.33 pixels/cycle for 24-bit RGB

- 0.25 pixels/cycle for 32-bit RGBA

- Half the number of pixels per cycle for 16 bits per channel

- Worst case throughput is 89% of nominal.

Deliverables

- Verilog RTL source code or targeted FPGA netlist

- Verilog can be made available on request

- Integration Test-Bench

- Simulation & synthesis scripts