Silicon IP Cores

PCI-M32MF

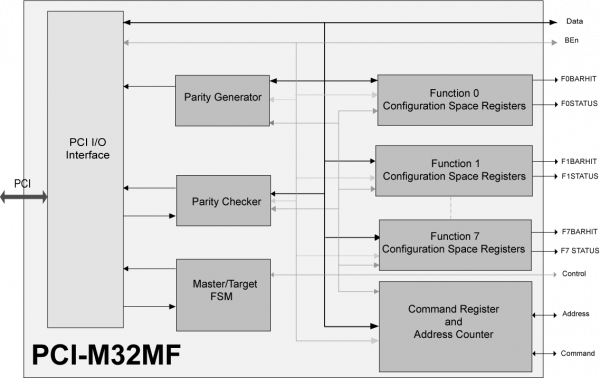

32-bit/33MHz Multi-Function PCI Master/Target

The PCI-M32MF implements a master/target PCI interface compliant with the PCI 2.3 specification. It supports a 32-bit address/data bus and operates up to 33 MHz PCI clock.

The core offers one to eight independent PCI functions in a single chip, each implementing 64 to 256 bytes of PCI Configuration Space registers as required. Each function supports up to six Base Address Registers, with both I/O and Memory space decoding from 16 bytes up to 4GB.

The PCI-M32MF builds on more than 15 years of CAST PCI IP expertise and has been designed for straightforward reuse, with proven design practices that ensure easy integration and smooth technology mapping. The core is available in synthesizable RTL or as a targeted FPGA netlist, and is delivered with everything required for rapid and successful integration and implementation.

The core has been verified through extensive simulation and rigorous code coverage measurements. It has also been implemented into a FPGA.

Support

The core as delivered is warranted against defects for ninety days from purchase. Thirty days of phone and email technical support are included, starting with the first interaction. Additional maintenance and support options are available.

Deliverables

The core is available in ASIC (synthesizable HDL) and FPGA (netlist) forms, and includes everything required for successful implementation. The ASIC version includes:

- HDL RTL source code

- Sophisticated HDL Testbench including vectors and ex-pected results

- Simulation script, vectors, expected results, and comparison utility

- Synthesis script

- Comprehensive user documentation, including detailed specifications and a system integration guide

The PCI-M32MF can be mapped to any ASIC technology or FPGA device (provided sufficient silicon resources are available). The following table provides sample results optimized for area with the core configured as follows: Function 0 with 2 BARs & Function 1 with 1 BAR. Please contact CAST to get characterization data for your target configuration and technology.

|

ASIC Technology |

Approx. |

Frequency |

| TSMC 0.18µm | 2932 gates | 66 |

| TSMC 0.13µm | 2860 gates | 66 |

| TSMC 90 nm | 2551 gates | 66 |

The PCI-M32MF can be mapped to any ASIC technology or FPGA device (provided sufficient silicon resources are available). The following table provides sample results configured with Function 0 with 2 BARs and Function 1 with 1 BAR. Please contact CAST to get characterization data for your target configuration and technology.

| Intel Device | LEs/ ALUTs |

Memory | I/Os | Fmax (MHz) |

Quartus |

| Cyclone-II EP2C5-8 |

925 | - | 53 | 33 | 8.1 |

| Cyclone-III EP3C10-8 |

935 | - | 53 | 33 | 8.1 |

| Stratix-II EP2S15-5 |

606 | - | 53 | 33 | 8.1 |

| Stratix-III EP3S50-4 |

604 | - | 53 | 33 | 8.1 |

The PCI-M32MF can be mapped to any ASIC technology or FPGA device (provided sufficient silicon resources are available). The following table provides sample results assuming that only the PCI I/Os are routed off-chip and the core is configured with 2 Base Address Registers for Function 0, and 1 Base Address Register for Function 1. Please contact CAST to get characterization data for your target configuration and technology.

| Family | Device | LUTs | BRAM | DSP | Fmax (MHz) |

| Artix-7 | 7a100t-2 | 1,096 | 2 | 0 | 33 |

| Kintex-7 | 7k160t-2 | 1,092 | 2 | 0 | 33 |

Features List

- Fully compliant with the PCI Local Bus Specification, Revision 2.3.

- 33 MHz performance

- 32-bit datapath

- Full Master/Target functionality, with support for these commands:

- Configuration Read, Configuration Write

Memory Read, Memory Write, Memory Read Multiple (MRM), Memory Read Line (MRL), Memory Write and Invalidate (MWI) - I/O Read, I/O Write

- Configuration Read, Configuration Write

- Zero wait states burst mode

- Support all interrupt pins (INTA#, INTB#, INTC#, INTD#)

- Type 0 Configuration space

- Support of all Base Address Registers

- Support of backend initiated target retry, disconnect and abort

- Parity generation and parity error detection

- Silicon-proven