Silicon IP Cores

QOID

QOI Lossless Image Compression Decoder

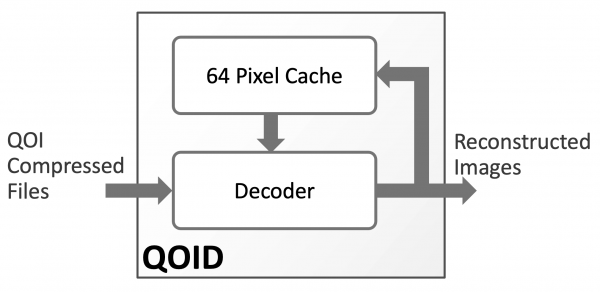

The QOID Core is a decoder that implements a highly efficient, low-power, lossless image decompression engine compliant with the Quite OK Image format (QOI) specification, version 1.0.

The QOI algorithm compresses RGB or RGBA images with 8 bits per color without any loss. It has a compression efficiency close to that of the PNG compression, at a fraction of the computational complexity. Capitalizing on the simplicity of the QOI algorithm, the QOID decoder core can decompress images at a very high speed and with minimal silicon resources.

The core occupies approximately 15,000 equivalent NAND2 gates and can decode one pixel per clock cycle. A single core instance can decompress images at rates sufficient for UHD 4k30 video even in low-end FPGAs, 4k60 in mid-range FPGAs, and 8k30 or 60 in modern ASIC technologies.

The QOID core is designed for ease of use and integration and adheres to coding and verification best practices. It requires no assistance from a host processor and uses simple handshake interfaces for input and output data. Technology mapping, timing closure, and scan insertion are trouble-free, as the core contains no multi-cycle or false paths, and uses only rising-edge-triggered D-type flip-flops, no tri-states, and a single-clock/reset domain. Its reliability and low risk have been proven through rigorous verification and FPGA validation.

The QOID is a digital core and can be mapped to any ASIC Technology device. The following are sample implementation results. These sample results do not represent the minimum area or the fastest clock speed for the QOID core. Please contact CAST to get accurate characterization for your target technology and throughput requirements.

| ASIC Technology | Area (um^2) | Eq. NAND2 Gates | Freq. (MHz) Mpixels/s |

|---|---|---|---|

| TSMC 28nm HPC tsmc28hpc-sc9-c35-ss-svt-125c |

7,267 | 14,418 | 1,400 |

| 6,371 | 12,640 | 1,000 | |

| TSMC 16nm tsmc16-sc7-svt-c16-ssgnp-125c |

3,009 | 17,413 | 1,700 |

| 2,380 | 13,777 | 1,000 |

The QOID is a digital core and can be mapped to any Altera® FPGA device (provided sufficient resources are available). The following are sample implementation results. These sample results do not represent the minimum area or the fastest clock speed for the QOID core. Please contact CAST to get accurate characterization for your target device and throughput requirements.

| Target Family/Device | Logic Resources |

Memory Resources * |

Freq. (MHz) Mpixels/s |

|---|---|---|---|

| AGILEX™ Speed grade -2 |

229 ALMs | 1 RAMB | 450 |

| Arria® 10 GX Speed grade -1 |

158 ALMs | 1 RAMB | 300 |

The QOID is a digital core and can be mapped to any AMD device (provided sufficient resources are available). The following are sample implementation results. These sample results do not represent the minimum area or the fastest clock speed for the QOID core. Please contact CAST to get accurate characterization for your target device and throughput requirements.

| Target Family/Device | Logic Resources |

Memory Resources |

Freq. (MHz) Mpixels/s |

|---|---|---|---|

| Kintex® UltraScale+™ xcku11pffve1517-3 |

199 LUTs | - | 750 |

| Kintex® UltraScale™ xcku085flvb1760-3 |

197 LUTs | - | 500 |

The QOID is a digital core and can be mapped to any Efinix FPGA device (provided sufficient resources are available). The following are sample implementation results. These sample results do not represent the minimum area or the fastest clock speed for the QOID core. Please contact CAST to get accurate characterization for your target device and throughput requirements.

| Target Family/Device | Logic Resources |

Memory Resources |

Freq. (MHz) Mpixels/s |

|---|---|---|---|

| Efinix Titanium Ti60F225-C4 |

383 XLRs | 3 Mem. Blocks | 300 |

| Efinix Trion T20F400-C4 |

383 LEs | 3 Mem. Blocks | 110 |

Engineered by Ocean Logic.

Features List

QOI Image Format

- Lossless compression

- Supports RGB and RGBA, 8-bit per color images

- Compression performance similar to that of PNG with a fraction of the computational complexity

QOID IP Core

- QOI decompression with a compact and high-throughput hardware decoder

- Receives raw header-less QΟΙ files

- Optional QOI header processing

- Supports RGB images

- RGBA support can be added on request

High-Throughput

- 1 pixel per clock-cycle throughput

- A single core can process UHD 4k60 in mid-range FPGAs, and 8k60 on modern ASIC technologies

Compact and Low-Power

- Approximately 15,000 gates

Deliverables

- VHDL or Verilog RTL source code or targeted FPGA netlist

- Verilog can be made available on request

- C-model for test vectors generation

- Integration Test-Bench

- Simulation & synthesis scripts

Resources

QOI Image Format page by the inventor Dominic Szablewski – phoboslab.org

Wikipedia entry on QOI Image Format

YouTube Video by Reducible on PNG and QOI