Silicon IP Cores

32-bit BA2X Processors

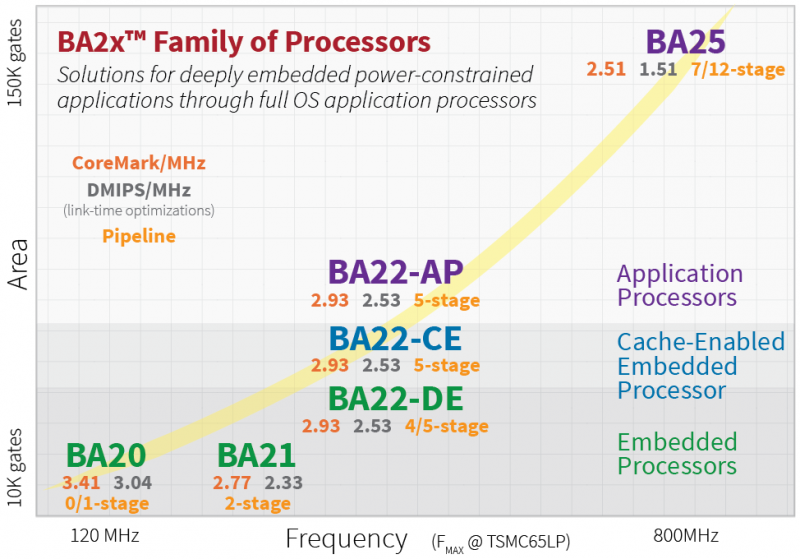

Royalty-free, code-dense, low-power MPUs

These BA2x Family processor cores are silicon-proven, royalty-free, easy to program, and technically competitive with traditional 32-bit processor choices.

Their BA2™ instruction set architecture yields extremely dense code, reducing memory and cache sizes, enabling fewer operations and more sleep, and cutting system-level energy consumption.

Various preconfigured versions bundle features and peripherals to target deeply embedded systems through application processors running Android or Linux.

All include the BeyondStudio™ IDE for quick programming, and reference designs, evaluation systems, and integration services are available.

- BA20: Ultra-low-power, efficient 32-bit processor with PipelineZero, for IoT with high code density.

- BA21: Low-power, 32-bit processor for deeply embedded systems, featuring two-stage pipeline and advanced power management.

- BA22-DE: Compact, configurable 32-bit processor with Harvard architecture for embedded applications, offering high clock frequencies.

- BA22-CE: Cache-enabled 32-bit processor for deeply embedded use, with low power consumption and high performance.

- BA22-AP: High-performance 32-bit processor for systems requiring off-chip memory, supports Linux/Android.

- BA25: High-performance 32-bit application processor with seven-stage pipeline, optimized for Linux and Android.

- Talos-BA2X: Evaluation kit for BA2X cores, including hardware, IDE, and example applications for comprehensive testing.

The BA2 ISA was developed to better exploit state-of-the-art compilers and deliver extreme code-density. Key features of the ISA are:

- Variable length instruction encoding

- 16-bit, 24-bit, 32-bit and 48-bit instructions

- Compiler chooses smallest suitable encoding

- Denser code than fixed-length ISAs

- 32 GPRs mean for less load/store

- Load/store ~25% of code for typical programs on RISC CPUs

- Single 24-bit function epilogue instruction, for restoring GPR values from the stack

- Rich set of arithmetic (including saturated), conditional branch and conditional move instructions

- DSP & Floating-Point extensions

Extreme code density reduces system-wide energy consumption, smaller code usually translates to:

- Smaller memories (non-volatile Flash/OTP and Shadow SRAMs)

- Less cache misses, and so less access to larger, power-hungry memories

- Fewer instructions to complete a specific task and longer sleep times

All BA2x processors are supported with development tools including a GCC/Eclipse IDE, libraries, architectural simulator, and reference design/eval system boards.

PipelineZero 32-bit Embedded Processor

32-bit Low-Power Deeply Embedded Processor

32-bit Deeply Embedded Processor

32-bit Cache-Enabled Embedded Processor

32-bit Basic Application Processor

32-bit Application Processor

Talos Evaluation Kit for BA2X Processor IP Cores