|

2024 was another successful year for CAST, with over 100 new customers licensing cores and enjoying CAST's Better IP Experience. We also established new partnerships with outstanding firms, launched several new products, and invested in growing the CAST engineering and sales teams.

In 2025, that investment will pay off for our customers with new automotive interface cores (starting with SafeSPI below), security cores (see PQC-KEM below), faster versions of our networking cores, Functional Safety ISO-26262 certification for additional cores, and other competitive new products in several areas.

Watch for new product announcements starting soon, and stop by to talk at upcoming events (listed down below). Or let us know which cores might help you have a successful 2025.

— Nikos Zervas, CEO

|

|

New SafeSPI Core Joins FuSa Product Line

|

|

|

|

Since the 1980s, the de facto Serial Peripheral Interface (SPI) standard has proven quite effective, especially in automotive systems where it typically links sensors with processors. Now this new core lets you retain the benefits of conventional SPI while gaining modern interoperability features and also addressing the growing requirement for automotive Functional Safety. Since the 1980s, the de facto Serial Peripheral Interface (SPI) standard has proven quite effective, especially in automotive systems where it typically links sensors with processors. Now this new core lets you retain the benefits of conventional SPI while gaining modern interoperability features and also addressing the growing requirement for automotive Functional Safety.

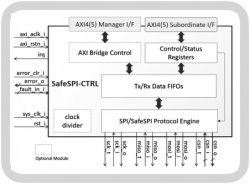

The new SafeSPI-CTRL SafeSPI Controller Core implements the Serial Peripheral Interface for Automotive Safety (SafeSPI), a formal industry standard developed and maintained by the SafeSPI Organization. This standard makes communication consistent, meaning the new core can work with any other SafeSPI-compliant devices (as well as older SPI devices). Most significantly, the SafeSPI protocol addresses Functional Safety by incorporating Cyclic Redundancy Check (CRC) for detec ting errors in data transmission command and response frames, strict handshaking mechanisms, and fault detection procedures. ting errors in data transmission command and response frames, strict handshaking mechanisms, and fault detection procedures.

Furthermore, the core internally employs modular redundancy, parity, and ECC to protect register files and memories and ensure compliance with the most stringent functional safety requirements. We believe it is the first such IP core, being fully featured and SafeSPI 2.0-compliant, ready for ASICs or FPGAs, and having the features required for ISO 26262 ASIL-D Functional Safety certification. Compliments to our development partner, Silesia Devices.

See more benefits in our press release, tech details on our product page, or just contact sales to start adding Functional Safety to your SPI connections today.

|

|

Prepare for Post-Quantum Cryptography

|

|

|

As quantum mechanics-based computers emerge, cryptography researchers are working to develop encryption and security solutions that can withstand the tremendous power of these new machines. Through our partnership with classical and post-quantum cryptographic (PQC) solutions developer KiviCore, we will soon ship CAST-quality IP cores that help you address these challenges. As quantum mechanics-based computers emerge, cryptography researchers are working to develop encryption and security solutions that can withstand the tremendous power of these new machines. Through our partnership with classical and post-quantum cryptographic (PQC) solutions developer KiviCore, we will soon ship CAST-quality IP cores that help you address these challenges.

Expected soon is the KiviPQC™-KEM core, a self-contained hardware/software codesign that implements the Module-Lattice Key Encapsulation Mechanism specified in the NIST FIPS 203 standard. It efficiently handles secret key generation, encapsulation, and decapsulation, enabling symmetric-key cryptographic algorithms to perform secure communication tasks such as authentication, data integrity verification, and encryption/decryption.

“We have managed to implement the secure key management functions needed for the post-quantum computing era in a high-quality IP core with a focus on resource efficiency, simplicity, and seamless integration. One of the earliest such IP cores available — and we believe the most reliable yet flexible — this is the first in our KiviPQC series that will dramatically simplify cryptographic system development in many fields.” “We have managed to implement the secure key management functions needed for the post-quantum computing era in a high-quality IP core with a focus on resource efficiency, simplicity, and seamless integration. One of the earliest such IP cores available — and we believe the most reliable yet flexible — this is the first in our KiviPQC series that will dramatically simplify cryptographic system development in many fields.”

— Frank Deicke, KiviCore co-founder

|

|

Choosing Lossless Data Compression Algorithms

|

|

|

Lossless data compression yields smaller data files or streams while ensuring that the original data can be fully and perfectly reconstructed. It is essential for applications demanding maximum data fidelity and helps reduce huge data volumes, optimize storage and bandwidth, reduce network latency, and save energy. Lossless data compression yields smaller data files or streams while ensuring that the original data can be fully and perfectly reconstructed. It is essential for applications demanding maximum data fidelity and helps reduce huge data volumes, optimize storage and bandwidth, reduce network latency, and save energy.

While the importance of lossless data compression is clear, how to choose the best of several algorithms — and then the best IP core for efficiently implementing that algorithm in hardware — is less so. Our Dr. Calliope-Louisa Sotiropoulou shed light on this with a comparison study she reported at December’s Design and Reuse IP-SoC Day in Grenoble.

Using a standard set of representative data files, she compared the compression ratio and speed and the computational complexity of popular algorithms GZIP, LZ4, Snappy, and Zstd. Check out her findings in this Battle of the Bits presentation. Spoiler alert: the best choice depends on the data and your system requirements, but there are smart strategies you can employ. See our Lossless Data Compression IP Cores, watch D&R’s Gabrielle Saucier interview Dr. Sotiropoulou in this video, and feel free to contact Dr. Sotiropoulou to learn more. Using a standard set of representative data files, she compared the compression ratio and speed and the computational complexity of popular algorithms GZIP, LZ4, Snappy, and Zstd. Check out her findings in this Battle of the Bits presentation. Spoiler alert: the best choice depends on the data and your system requirements, but there are smart strategies you can employ. See our Lossless Data Compression IP Cores, watch D&R’s Gabrielle Saucier interview Dr. Sotiropoulou in this video, and feel free to contact Dr. Sotiropoulou to learn more.

|

|

Time for TSN Ethernet IP Cores

|

|

|

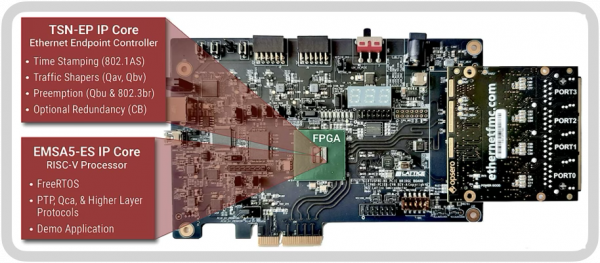

With its fast deterministic communication, Time Sensitive Networking (TSN) is rapidly reshaping system architectures in automotive, aerospace, and other domains. Working with our partner Fraunhofer IPMS — a TSN pioneer — our TSN cores date back to 2018. Having gone through multiple industry plugfests and numerous customer deployments these are probably the most proven such IP cores available. We currently offer: With its fast deterministic communication, Time Sensitive Networking (TSN) is rapidly reshaping system architectures in automotive, aerospace, and other domains. Working with our partner Fraunhofer IPMS — a TSN pioneer — our TSN cores date back to 2018. Having gone through multiple industry plugfests and numerous customer deployments these are probably the most proven such IP cores available. We currently offer:

These achieve highly accurate timing synchronization, schedule traffic with minimum latency, are technology-agnostic, and use a fraction of the silicon resources of competing IP cores (see representative results for ASICs and multiple FPGA vendor devices on the linked pages).

As part of our decades-long partnerships with each of the FPGA vendors, we were recently invited to participate in the Lattice Developer’s Conference. There our Alex Mozgovenko and Evan Price presented a live demo of our TSN Ethernet Endpoint core running on a Lattice CertusPro™-NX platform board along with the Functional Safety RISC-V EMSA5-FS processor we offer.

The demo showed accurate timing synchronization between networked devices (802.1AS); flexible traffic shaping (8021.Qav & 802.1Qbc) with pre-emption support (802.Qbu & 802.3br); and optional redundancy (802.1CB) and path control & reservation (802.1Qca). Watch the video on the Lattice DevCon site then contact Alex with any questions.

|

|

|

|

|