Silicon IP Cores

8051s in Modern Systems: Interfacing to AMBA Buses

Peter Dumin, CAST Senior Account Manager

Despite being 40 years old, 8051 microcontrollers can still serve useful roles in modern systems.

But integrating 8051s in today's systems with their de facto standard AMBA® buses, wider datapaths, and shared memories can seem impossible. Yet it can be done. Here we take a look at the challenges, and how to overcome them.

Why Use 8051s?

First, why should you even consider using an 8-bit 8051-compatible microcontroller?

A primary reason is to more efficiently handle useful functions in certain ultra-low-power systems, such as for edge-device Internet of Things applications. Consider:

- The 8-bit 8051 will be considerably smaller than any 32-bit counterpart. Less silicon area means less power leakage, a critical factor for devices with long idle times.

- Code for the 8051’s 8-bit Complex Instruction Set Architecture (CISC) can be smaller and more dense than that for today’s more popular Reduced Instruction Set Architecture (RISC) processors. This means smaller memories—further reducing area-dependent leakage— and also, significantly, fewer energy-consuming instruction fetches to complete a given task.

- Developer training and 8051 deployment and testing are simplified through a vast, robust ecosystem of 8051 development and debugging tools, software stacks, example code, and general support.

- There are numerous thoroughly proven 8051 microcontroller IP cores available that integrate peripherals—SPI, I2C, UARTs, etc.—in a package that can be reliably dropped into many systems.

With these advantages, why aren’t 8051s used as often as they once were?

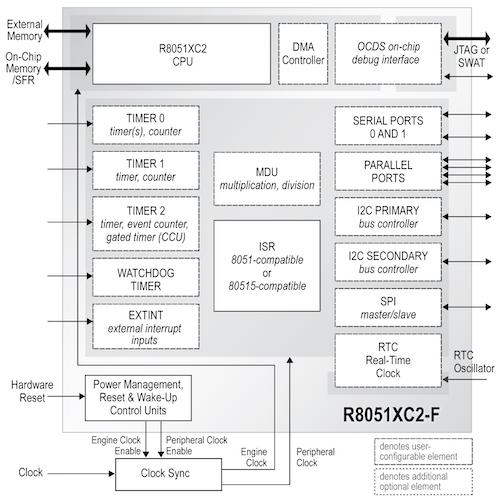

Figure 1 - Typical 8051 IP core, with External Memory and SFR bus interfaces and multiple integrated peripherals. (From CAST R8051XC2 High-Performance, Configurable 8-bit Microcontroller.)

8051 Integration Challenges

The answer lies not so much in the functionality of the 8051 itself, but rather in the apparent difficulties integrating an 8051 in a modern SoC. AMBA buses dominate in these systems, but the original 8051 knows nothing about AXI, AHB, APB, or the other AMBA variations.

Examining a classic 8051, we seen it has two main external buses:

- The tightly-coupled, directly-addressable Special Function Registers (SFR) bus for communication between the CPU and peripherals, and

- The pointer-addressable External Data Memory bus.

Each of these buses is asynchronous and only 8-bits wide. In contrast, AMBA buses are 32- or 64-bits wide (or even wider) and are synchronous with control flow. How can a system architect overcome these differences?

Using an 8-Bit Bus in a Wider Bus World

A bus adapter is the key to integrating the 8051’s 8-bit bus with 32- or 64-bit AMBA buses.

For read operations, the bus adapter feeds the 8051 the correct byte out of the wider, multi-byte word it reads on the AMBA bus. For write operations, the adapter replaces the 8-bit write accesses on the 8051 bus with read-modify-write accesses on the wider bus.

The complexity of adding such a bus adapter may sound too much to deal with, but fortunately, this is greatly reduced for the more recent incarnations of AMBA buses, e.g., APB5, AXI4, and AXI4-Lite. These include byte qualifier signals, eliminating the need for the read-modify-write operations on the AMBA side.

8051 IP cores providing an 8-bit to wider bus adapter typically do so in the form of a simple wrapper around the base 8051 core. Such a wrapper — typically an optional feature — simplifies both the integration and operation of the 8051.

Fitting Asynchrony in a Synchronous System

While a proper bus adapter can deal with differing data path widths, timing remains an issue.

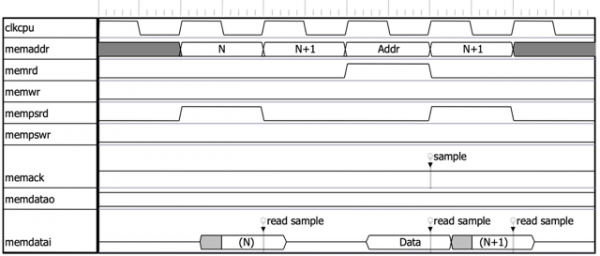

A native 8051 interface performs a read or write operation in a single clock cycle. It provides both address and data information in that one phase. (See example in Figure 2.)

Figure 2 — 8051 external memory READ cycle. (From CAST R8051XC2 Design Specification, Figure 22)

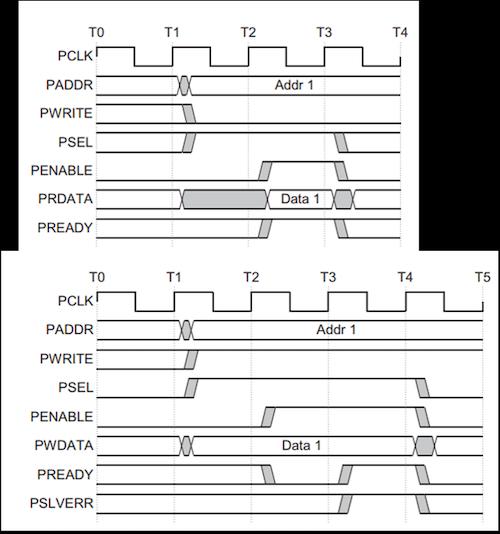

In contrast, AMBA AHB, APB, or AXI4-Lite buses require multiple clock cycles to perform the same operation, separately specifying the address and the data. Specifically, AHB requires two phases — for address and for data — while APB introduces a minimum two-cycle access using the PSEL/PENABLE signals. (See Figure 3.) Further complicating things, the AMBA standards allow the subordinate (slave) to control the flow of accesses by means of a ready signal.

Figure 3 - AMBA APB external memory Read transfer timing without and with WAIT states. (From APB Protocol.)

This timing discrepancy between 8051s and AMBA buses is practically impossible to overcome in the general case.

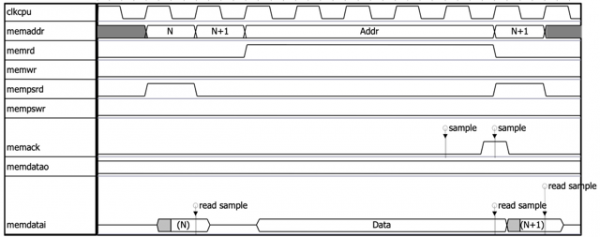

But some 8051 cores manage to do it by implementing an acknowledge signal allowing the extension of the read or write access cycles, as shown in Figure 4. With this addition, the 8051 can now wait until the bus slave accepts the write data or returns the read data. This in turn makes it possible to bridge the timing variation between the 8051 bus and an AMBA bus.

Figure 4 — 8051 extended external memory Read cycles. (From CAST R8051XC2 Design Specification, Figure 24.)

Conclusions: Evaluating 8051 IP for Modern Systems

There are power (and cost) benefits to be had in selectively using 8051s for certain housekeeping functions, sensor interfaces, and other operations in a modern AMBA bus-based system. You can overcome the apparent integration challenges by evaluating each 8051 IP core you consider:

- Does it have a native APB/AHB interface?

- Does it offer a bridging option?

- Does it use wait-state inputs, making it possible to use a wrapper?

- Does it have an SFR interface capable of interfacing with APB and similar?

If a given 8051 IP core lacks these features, look elsewhere.

Or you might simplify your 8051 IP selection by looking at the royalty-free ASIC and FPGA 8051 cores we at CAST offer. Several variations are available to optimally satisfy your requirements, including the tiny T8151XC3, the super-fast S8051XC3, and the mature R8051XC2.

All these 8051 IP cores include a configurable set of peripherals, have data-ready/acknowledge signals to support access flow control on both the SFR and the external memory buses, and can optionally be delivered with bridges to AMBA buses with or without a clock domain crossing (CDC) boundary. Plus, you get rapid, expert technical support from the most experienced 8051 team on the planet, helping customers as far back as 25 years ago up through today’s smart system architects who are still exploiting the benefits of 8051 MCUs.